### **Outline of Chapter 4**

- 1- Intro to MOS Field Effect Transistor (MOSFET)

- 2- NMOS FET

- 3- PMOS FET

- 4- DC Analysis of MOSFET Circuits

- 5- MOSFET Amplifier

- 6- MOSFET Small Signal Model

- 7- MOSFET Integrated Circuits

- <u>8- CSA, CGA, CDA</u>

- 9- CMOS Inverter & MOS Digital Logic

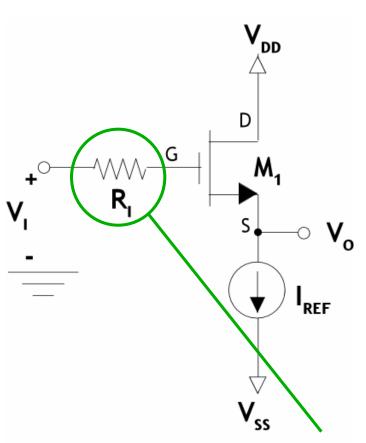

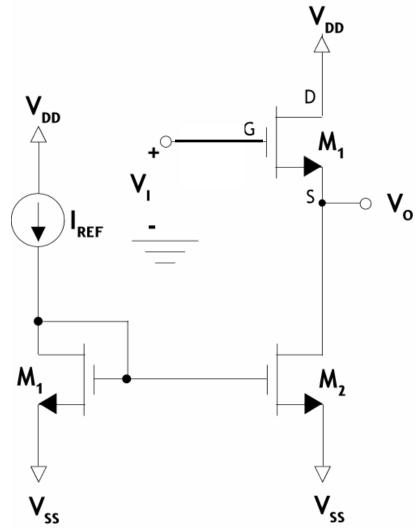

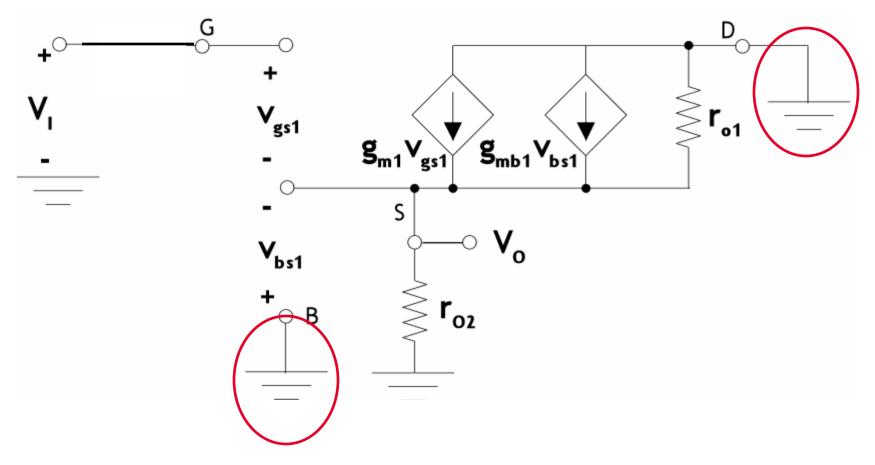

# McGill Department of Electrical and Computer Engineering **Common Drain Amplifier (CDA)**

- A nMOS current mirror is used as I<sub>REF</sub> including the output resistance.

- Voltage signal source DCcoupled to gate terminal

- Drain terminal held at a DC voltage

- Since source terminal not at signal ground, Body effect exists

$R_{I}$  is the resistance from previous stage

- Replace with a "real" current source including output resistance r<sub>o2</sub>

- No problem including AC CLM

- Two types of analysis:

Neglect AC Body-Effect

**Use AC Body-Effect**

#### **CDA Without Body Effect**

$$A_{V} = \frac{v_{o}}{v_{I}} = \frac{r_{o2} \| r_{o1}}{r_{o2} \| r_{o1} + \frac{1}{g_{m1}}}$$

$$R_{IN} \Rightarrow \infty$$

$$R_{OUT} = r_{o1} \| r_{o2} \| \frac{1}{g_{m1}} \|$$

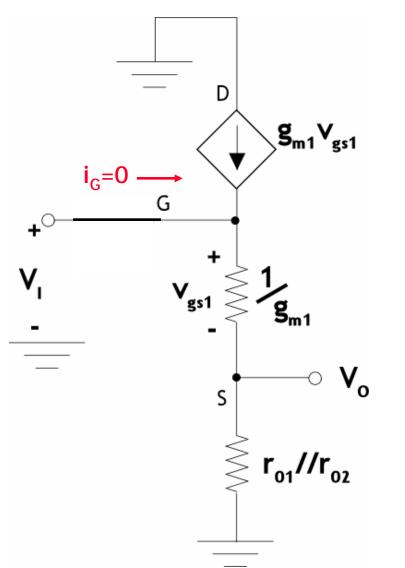

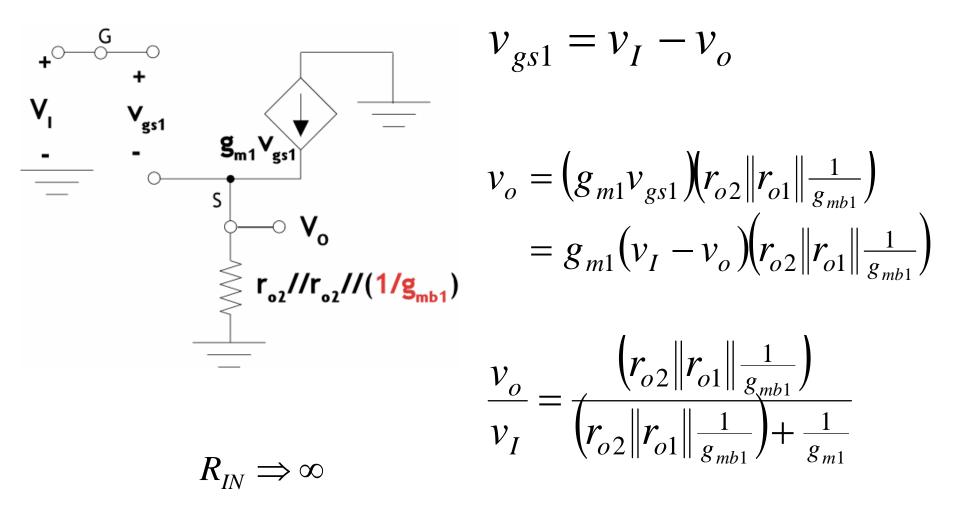

### **CDA With Body Effect**

### **CDA With Body Effect**

# **CDA With Body Effect - R**<sub>OUT</sub>

Short input voltage source  $v_{gs1} = -v_x$  $v_x = (g_{m1}v_{gs1} + i_x)(r_{o2}||r_{o1}|| \frac{1}{g_{mb1}})$ S  $\frac{1}{v_{x}} R_{OUT} = \frac{v_{x}}{i_{x}} = \frac{r_{o2} \|r_{o1}\| \frac{1}{g_{mb1}}}{1 + g_{m1} (r_{o2} \|r_{o1}\| \frac{1}{g_{mb1}})}$ By source-absorption:

$R_{OUT} = r_{o1} // r_{o2} // (1 / g_{m1}) // (1 / g_{mb1}))$

### **Outline of Chapter 4**

- 1- Intro to MOS Field Effect Transistor (MOSFET)

- 2- NMOS FET

- 3- PMOS FET

- 4- DC Analysis of MOSFET Circuits

- 5- MOSFET Amplifier

- 6- MOSFET Small Signal Model

- 7- MOSFET Integrated Circuits

- 8- CSA, CGA, CDA

- <u>9- CMOS Inverter & MOS Digital Logic</u>

V<sub>DD</sub>

S

D

D

G

G

V<sub>I</sub> C

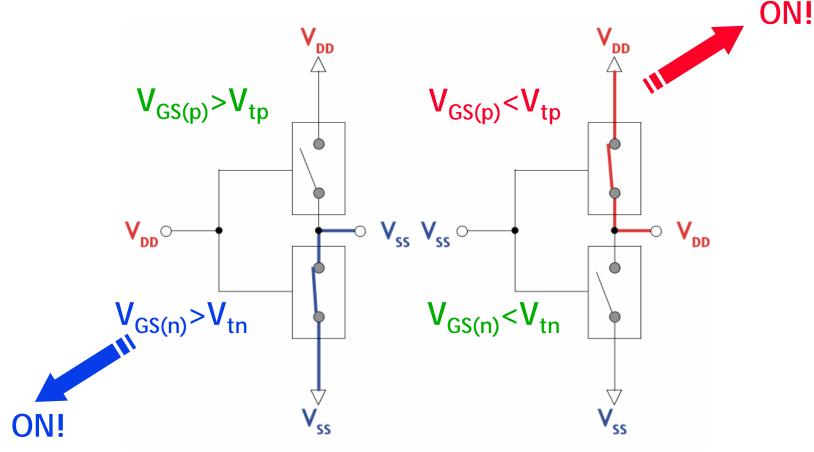

# **CMOS Inverter**

- MOSFETs can act as almost ideal current switches with symmetric VTCs.

- Matching of  $M_P$  and  $M_N$ :  $|V_{tP}| = V_{tN} = V_t$

- Since typically k<sup>'</sup><sub>P</sub> is 2-3 times smaller than k<sup>'</sup><sub>n</sub>, the widths of the transistors are used to compensate:

$$W_P = 3W_N \quad \square \qquad > \quad k'_p \frac{W_P}{L_P} = k'_n \frac{W_N}{L_N}$$

This is definition of matched devices; equal current driving and sinking capabilities when charging & discharging capacitive loads

#### **CMOS Inverter – Operation**

nMOS transistor pulls output voltage to the most negative rail. pMOS transistor pulls output voltage to the most positive rail. MOSFETs 10

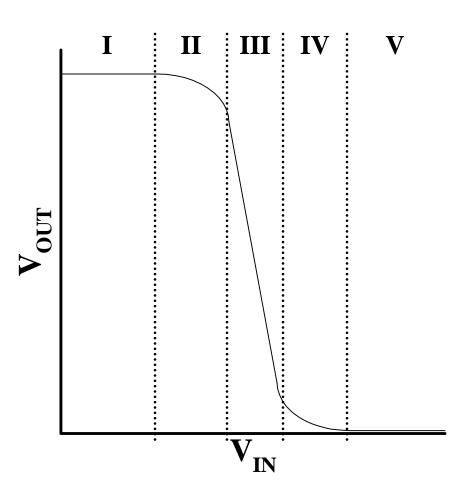

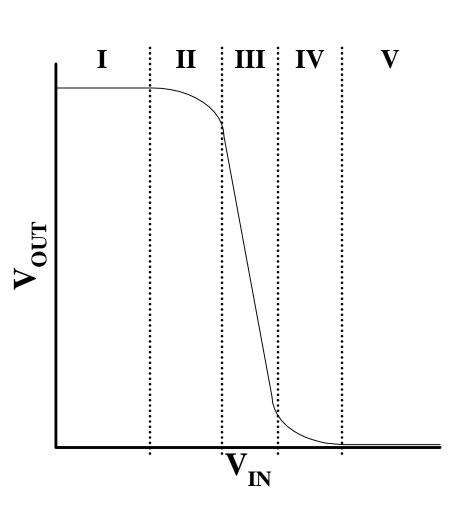

#### **Inverter VTC**

- Region I:  $V_{IN} < V_t$

- M<sub>N</sub> cutoff, M<sub>P</sub> in triode

- Low-resistance path from  $V_{DD}$  to  $V_{OUT}$  pulls output high

- No current flow

- Region II:  $V_{IN} > V_t$

- M<sub>N</sub> enters saturation

- M<sub>P</sub> still in triode

- Current flows,

V<sub>OUT</sub> starts to fall

- Region III:

- High-gain region

- M<sub>N</sub> & M<sub>P</sub> saturated

- VTC slope = gain  $_{M}$

#### **Inverter VTC**

- Region IV:

- M<sub>N</sub> enters triode

- M<sub>P</sub> still in saturation

- Region V:  $V_{IN} > V_{DD} V_t$

- $M_P$  cutoff,  $M_N$  in triode

- Low-resistance path from

V<sub>OUT</sub> to ground pulls output low

- No current flow

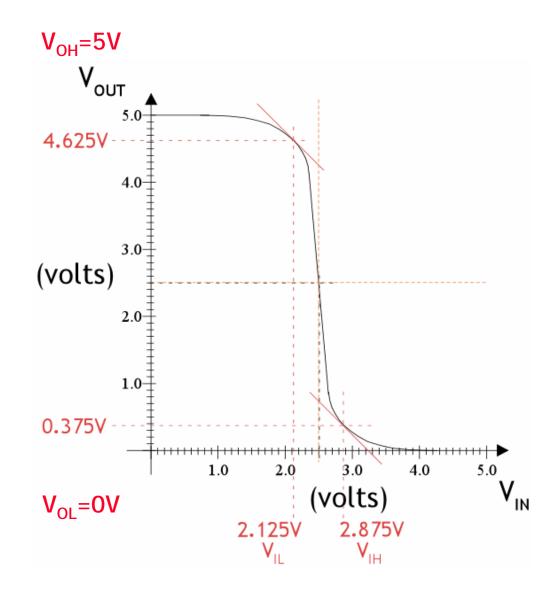

#### **VTC Characteristics**

- A matched inverter has symmetric voltage transfer characteristic.

- V<sub>OL</sub> and V<sub>OH</sub> are defined as 0V and 5V respectively.

- $V_{IH}$  and  $V_{IL}$  defined as location where VTC slope = -1

- V<sub>IL</sub> is in region II

- V<sub>IH</sub> is in region IV

# Finding $V_{IH}$ – Matched Devices

• In region IV,  $M_P$  saturated,  $M_N$  in triode:

$$k_{P} \underbrace{W_{N}}_{N} \left[ (V_{IN} - V_{t}) V_{OUT} - \frac{1}{2} V_{OUT}^{2} \right] = \frac{1}{2} k_{P} \underbrace{W_{P}}_{N} (V_{IN} - V_{DD} + V_{t})^{2}$$

$$(V_{IN} - V_t)V_{OUT} - \frac{1}{2}V_{OUT}^2 = \frac{1}{2}(V_{IN} - V_{DD} + V_t)^2$$

(1)

•  $V_{IN} = V_{IH}$  when  $\frac{\partial V_{OUT}}{\partial V_{IN}} = -1$  .: Take derivative wrt  $V_{IN}$

$$V_{OUT} + \left(V_{IN} - V_t\right) \frac{\partial V_{OUT}}{\partial V_{IN}} - V_{OUT} \frac{\partial V_{OUT}}{\partial V_{IN}} = \left(V_{IN} - V_{DD} + V_t\right)$$

• Substitute  $V_{IN} = V_{IH}$  & simplify to get:  $V_{OUT} = V_{IH} - \frac{V_{DD}}{2}$

# Finding $V_{IH}$ – Matched Devices

• Take result for  $V_{OUT}$  when  $V_{IN} = V_{IH}$

$$V_{OUT} = V_{IH} - \frac{V_{DD}}{2}$$

• Substitute into ①

$$\left(V_{IH} - V_t\right)\left(V_{IH} - \frac{V_{DD}}{2}\right) - \frac{1}{2}\left(V_{IH} - \frac{V_{DD}}{2}\right)^2 = \frac{1}{2}\left(V_{IH} - V_{DD} + V_t\right)^2$$

• Solving for  $V_{IH}$ , get:  $V_{IH} = \frac{1}{8} (5V_{DD} - 2V_t)$

# Finding $V_{IL}$ – Matched Devices

- Can use similar procedure to find  $V_{IL}$

- Write equations for region II operation:  $M_P$  in triode,  $M_N$  in saturation

- Solve for  $V_{OUT}$  when  $V_{IN} = V_{IL}$  and substitute back into equations and solve for  $V_{IL}$

$$V_{IL} = \frac{1}{8} \left( 3V_{DD} + 2V_t \right)$$

- Result:

- Alternatively, can find  $V_{IL}$  using symmetry of VTC because  $V_{IL}$  and  $V_{IH}$  are symmetric about  $V_{DD}/2$

$$V_{IH} - \frac{V_{DD}}{2} = \frac{V_{DD}}{2} - V_{IL}$$

### **Noise Margins**

NM<sub>H</sub>, High Noise Margin Definition:

$$NM_{H} = V_{OH} - V_{IH} = V_{DD} - V_{IH} \qquad V_{IH} = \frac{1}{8} (5V_{DD} - 2V_{t})$$

$$NM_{H} = V_{OH} - V_{IH} = \frac{1}{8} (3V_{DD} + 2V_{t})$$

NM<sub>L</sub>: Low Noise Margin Definition:

$$NM_{L} = V_{IL} - V_{OL} = V_{IL} - 0 \qquad V_{IL} = \frac{1}{8} (3V_{DD} + 2V_{t})$$

$$NM_{L} = V_{IL} - V_{OL} = \frac{1}{8} (3V_{DD} + 2V_{t})$$

Conclusion: NMs equal for matched devices (Problem 4.107) MOSFETs 17

### **Mismatched Inverter Characteristics**

• For mismatched devices:

$$\left|V_{tp}\right| \neq V_{tn}$$

$k'_{p} \frac{W_{P}}{L_{P}} \neq k'_{n} \frac{W_{N}}{L_{N}}$

- VTC not symmetric any longer

- $V_{IL}$  and  $V_{IH}$  can be found using same approach as before, with more algebra

- Resulting VTC noise margins will not be equal, but  $V_{OH}$  and  $V_{OL}$  will be unchanged

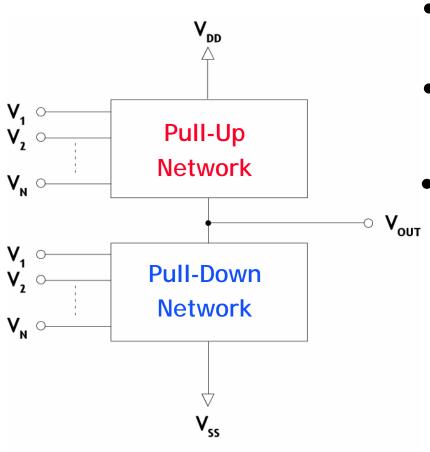

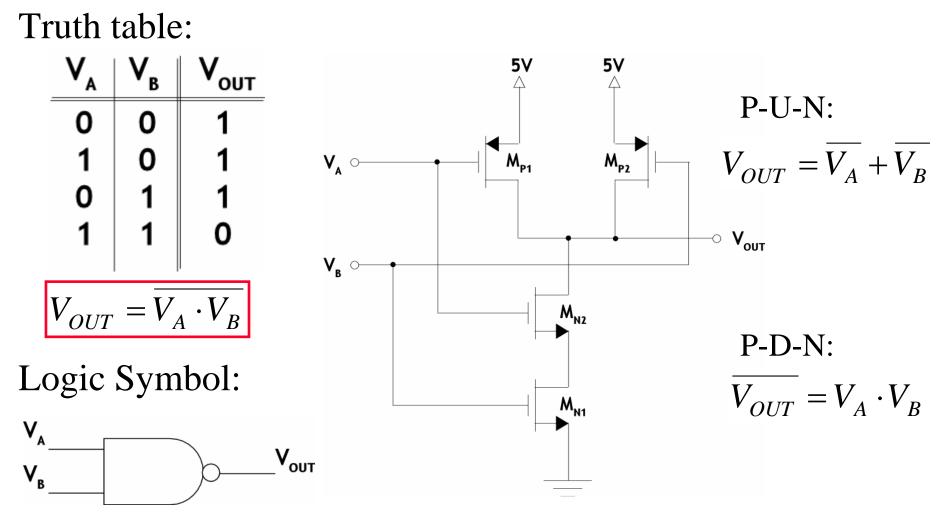

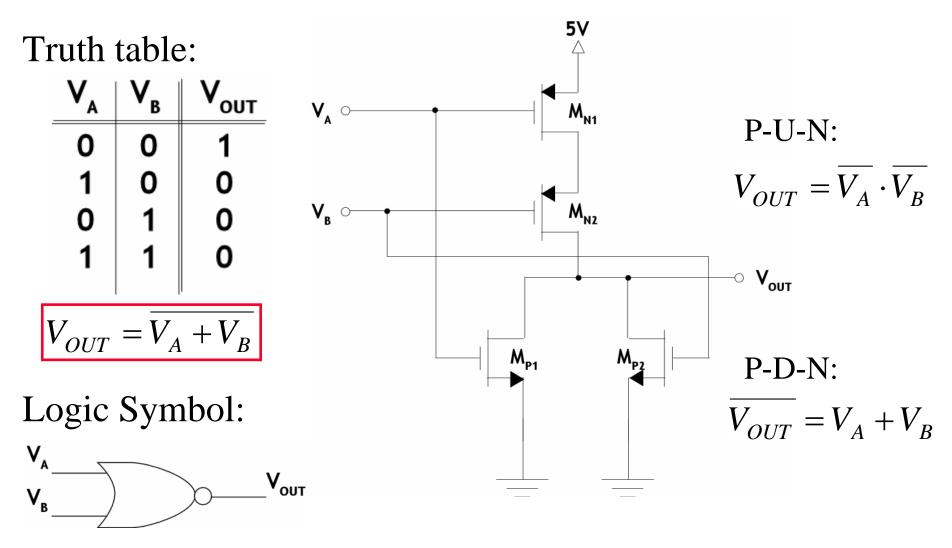

# **Structure of CMOS Logic-Gates**

- P-U-N: pull-up network (PMOS transistors)

- **P-D-N: pull-down network** (NMOS transistors)

- P-U-N & P-D-N almost invariably made *complementary* networks

- i.e. series-connected transistors in one network are parallelconnected in the other & vice versa

- Facilitates formal design and logic synthesis techniques MOSFETs 19

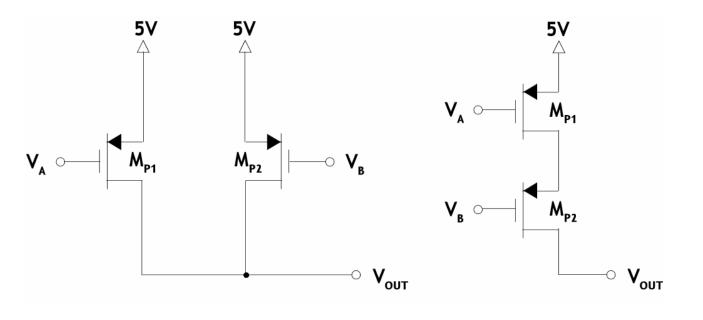

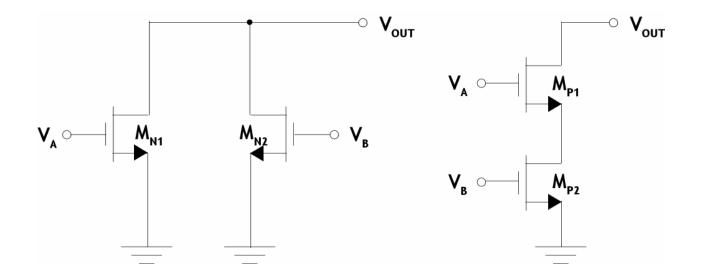

#### **Basic Pull-Up Structures**

Parallel Structure  $V_A or V_B$  is low

$$V_{OUT} = \overline{V_A} + \overline{V_B}$$

Serial Structure  $V_{OUT}$  is high when *either*  $V_{OUT}$  is high when *both*  $V_A$ and  $V_{\rm B}$  are low

$$V_{OUT} = \overline{V_A} \cdot \overline{V_B}$$

#### **Basic Pull-Down Structures**

Parallel Structure  $V_A or V_B$  is high

$$\overline{V_{OUT}} = V_A + V_B$$

Serial Structure  $V_{OUT}$  is low when *either*  $V_{OUT}$  is low when *both*  $V_A$ and  $V_{\rm B}$  are high

$$\overline{V_{OUT}} = V_A \cdot V_B$$

### **2-Input CMOS NAND Gate**

#### **2-Input CMOS NOR Gate**

### **Outline of Chapter 4, Sections 4.8-4.9**

- 1- High-Frequency Model of MOSFET

- 2- Frequency Response of CSA

- Note: Frequency response of CGA and CDA are covered in EC2

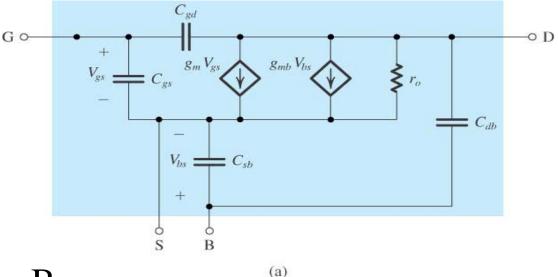

# **High-Frequency Model**

- The small signal model discussed so far didn't include internal capacitances and resulted in constant gain without accounting for frequency changes.

- Internal capacitances:

- The gate capacitive (Cox) effect is modeled by three capacitors Cgs, Cgd and Cgb

- The source-body and drain-body depletion layer capacitances: Reverse biased pn junctions

# **Gate Capacitive Effect**

• In Triode region the channel has a uniform depth:

$$C_{gs} = C_{gd} = \frac{1}{2} WLC_{ox}$$

• In saturation region: Channel is pinched off:

$$C_{gs} = \frac{2}{3} WLC_{ox} \qquad \qquad C_{gd} = 0$$

• In the cutoff region:

$$C_{gs} = C_{gd} = 0$$

- Often there is overlap area underneath the gate in the S and D diffusion (n<sup>+</sup> or P<sup>+</sup>) regions.

- This adds to Cgs and Cgd

### **Junction Capacitances**

- The two pn junction in MOSFET are reverse biased, so the depletion regions creates junction capacitances

- Junction capacitance in a reverse-biased diode or pn junction is defined by:

$$C_{j} = \frac{C_{j0}}{\left(1 + \frac{V_{R}}{V_{0}}\right)^{m}} \qquad \frac{1}{3} \le m \le \frac{1}{2} \qquad C_{j} = \frac{C_{j0}}{\sqrt{1 + \frac{V_{R}}{V_{0}}}}$$

• Where V0 is the junction built-in voltage, Cj0 is the value of Cj when zero voltage is applied and m is the grading coefficient

## **Junction Capacitances**

• The two junction capacitances in MOSFET are:

$$C_{sb} = \frac{C_{sb0}}{\sqrt{1 + \frac{V_{SB}}{V_0}}} \qquad \qquad C_{db} = \frac{C_{db0}}{\sqrt{1 + \frac{V_{DB}}{V_0}}}$$

- Assuming m=1/2

- V0 is the junction built-in voltage (0.6 to 0.8 V)

- Csb0 is the value of Csb at VSB=0

- Cdb0 is the value of Cdb at VDB=0

- Formulas are for small-signal operation

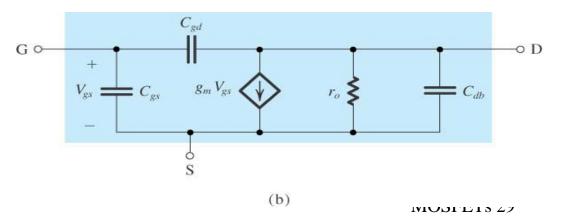

# **High-Frequency MOSFET Model**

• Complete Model used in SPICE (Fig. 4.47):

• When S is connected to B:

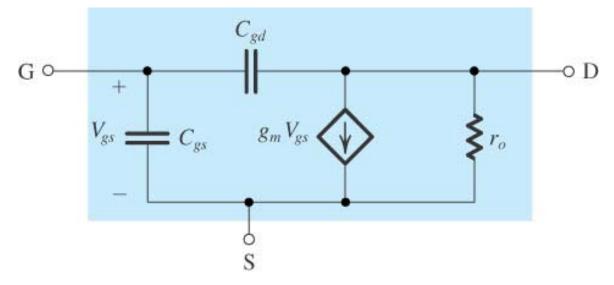

# **High-Frequency MOSFET Model**

• Capacitance  $C_{db}$  is usually neglected and for hand calculations and circuit solutions the following model is used

• Note: Hybrid- $\pi$  model is used

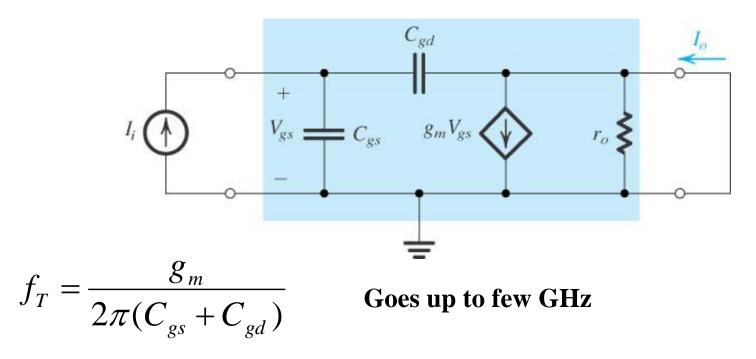

# **MOSFET Unity-Gain Frequency**

- Unity-gain frequency,  $f_T$ , is a figure of merit for high-frequency operation.

- It is defined as the frequency at which the short circuit current gain in the Common Source amplifier is 1.

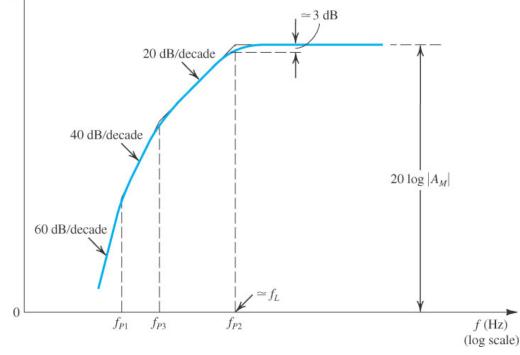

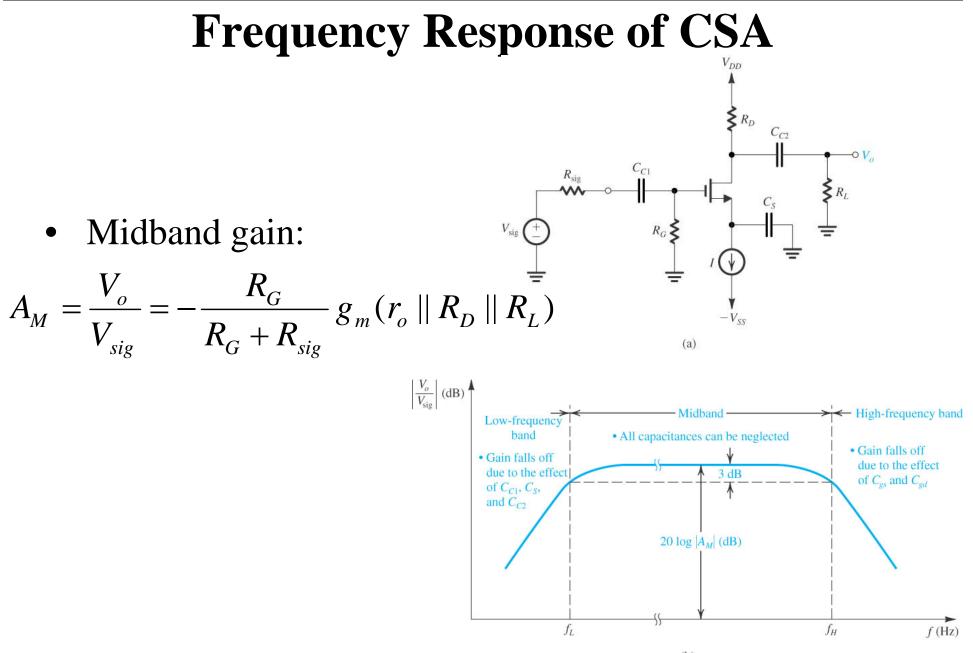

# **Frequency Response of CSA**

- Gain expressions derived previously were assumed to be independent of frequency.

- In reality gain is constant only over the midband frequencies

- The midband gains are the gain relations we found earlier

- Low frequency falloff is due to coupling and bypass capacitors

- High frequency gain falloff is due to internal capacitances.

# **High-Frequency Response (CSA)**

- $f_H$  and  $f_L$  are frequencies at which gain is 3 dB lower than the midband value

- 3dB bandwidth is:

$$BW \equiv f_H - f_L$$

- $BW \cong f_H$ • If  $f_I \ll f_H$  then

- Another figure of merit for an amplifier is gain-bandwidth  ${\color{black}\bullet}$ product

$$GB \equiv \left| A_{M} \right| BW$$

D

$r_o \lesssim$

$R_D$

$R'_{i}$

$R_L$

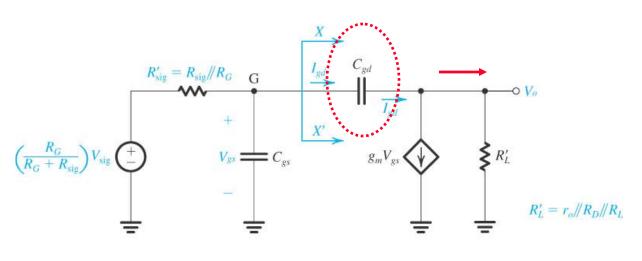

### **High-Frequency Response (CSA)**

$R_{\rm sig}$

~~~

$V_{\rm sig}$

$R_G$

• CSA

• Using Thevenin Theorem

S

(a)

$g_m V_{gs}$

G

$= C_{gs}$

$R'_L$

### **High-Frequency Response (CSA)**

• Lowpass STC circuit  $R'_{sig}$  G  $V_o = -g_m R'_L$

$= C_{es}$

Miller Effect

• Corner frequency

$$\omega_{H} = \omega_{0} = \frac{1}{C_{in}R_{sig}'} = \frac{1}{(C_{gs} + C_{eq})R_{sig}'}$$

$C_{eq} = C_{gd} \left( 1 + g_m R_L' \right)$

$g_m V_{es}$

• High-frequency gain of CSA

$\left(\frac{R_G}{R_G + R_{\rm sig}}\right) V_{\rm sig}$

$$\frac{V_o}{V_{sig}} = \frac{A_M}{1 + \frac{s}{\omega_H}} = -\frac{R_G}{R_G + R_{sig}} (g_m R'_L) \frac{1}{1 + \frac{s}{\omega_H}}$$

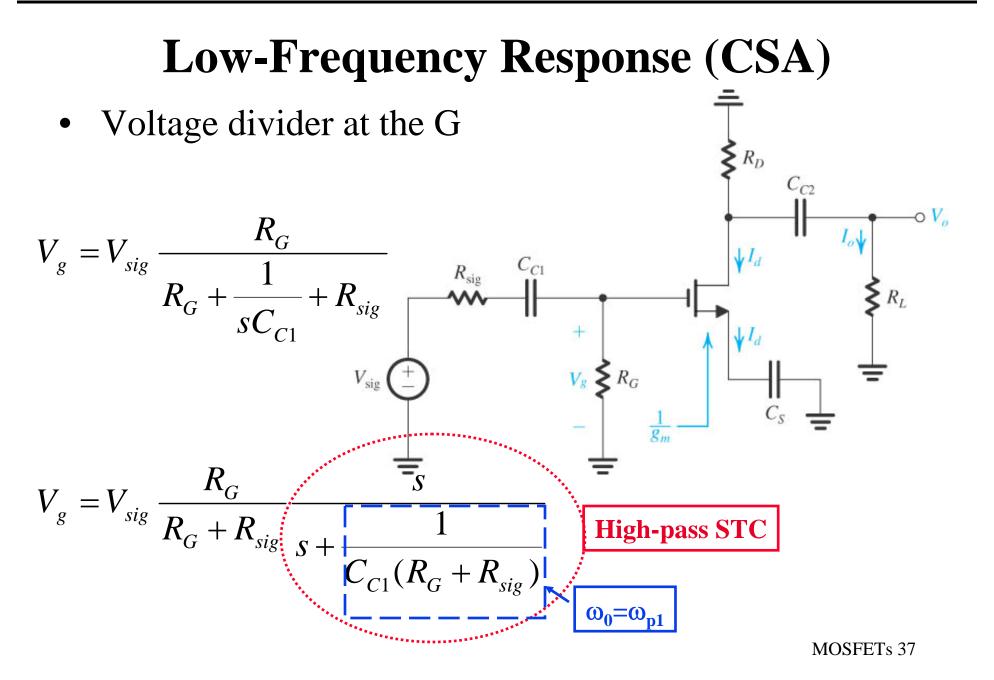

### Low-Frequency Response (CSA)

- Two other high-pass factors are due to:

- Source bypass capacitance

- Load coupling capacitance

$$\omega_{p2} = \frac{g_m}{C_s}$$

$$\omega_{p3} = \frac{1}{C_{C2}(R_D + R_L)}$$

• Low-frequency transfer function or low-frequency gain of CSA

$$\frac{V_o}{V_{sig}} = -\frac{R_G}{R_G + R_{sig}} (g_m R_D \parallel R_L) \frac{s}{s + \omega_{P1}} \frac{s}{s + \omega_{P2}} \frac{s}{s + \omega_{P3}}$$

## Low-Frequency Response (CSA)

- To find the time constant for poles  $f_{p1}$ ,  $f_{p2}$  and  $f_{p3}$

- Set source to zero

- Consider each C separately (others are short circuit)

- Find the total resistance seen between the two terminals of C  $\left|\frac{V_o}{V_{sig}}\right|^{(dB)}$